| | ホーム | 私の電子工作作品集 |

| [ 初公開日:2013年6月17日 ] |

|

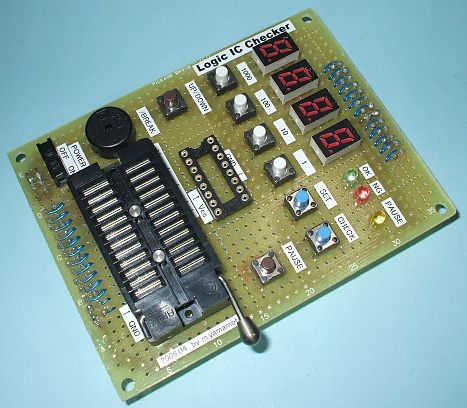

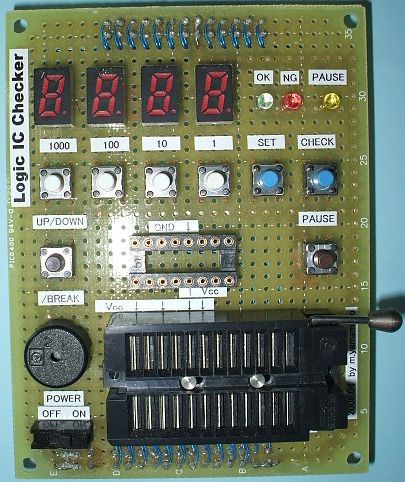

74シリーズ、4000シリーズ、4500シリーズのC−MOS ICに対応した、汎用ロジック IC チェッカーです。 74シリーズのスタンダード・LSなどの、一部のTTLに対応できるものもあります。 この作品は、サイト "黒猫電脳研究室" で紹介されていたものに触発され、ぜひ私も、自分なりのオリジナルなものを作ってみたくて 作製をしたものです。

"黒猫電脳研究室" では、H8/3052F CPUおよび C を使用して作製されていますが、ここでは3個のPIC (PIC16F628A, PIC16F877A, PIC18F452) および アセンブラを使用しています。 したがって、ハードウェア構成、ソフトウェアともに、"黒猫電脳研究室" とはまったく異なったものになっています。 【 お知らせ 】 最近、このページをご覧になっていただける方々が急増してきました。 作者の私にとってこんなに嬉しいことはなく、大きな励みになっています。 本当にありがとうございます。 そんな方々に、心を込めてのお知らせです。 先にお知らせをしたように "180. ロジック IC チェッカー II" の準備が整い、ようやく公開することができました。 このページで紹介をしている "ロジック IC チェッカー" の 12年ぶりのリメイク版で、最大の特徴は外観を大きく変更した点でまったくの別物となっています。 勿論、内部的にも変更をした点は多く、ぜひ新しいページの "プログラム" の項をご覧になって下さい。 |

|

| 回路図 (LogicIC_Checker.CE3) | ページトップ |

< 回路参考 >

| 特殊電源ピン・ソケットアダプタについての説明や使用方法については、特殊電源ピン・ソケットアダプタ の項を参照のこと。 |

|

| 回路図 (SpcSocket.CE3) | ページトップ |

|

|

|

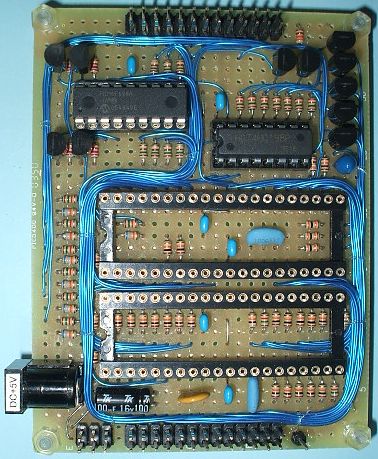

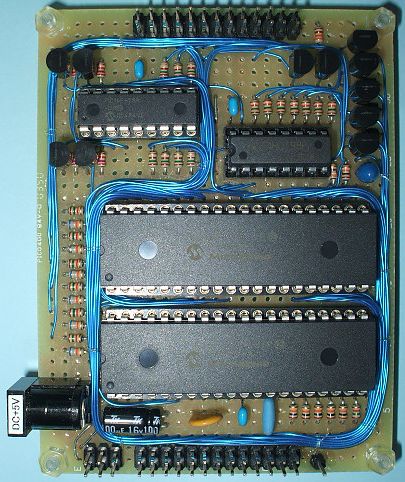

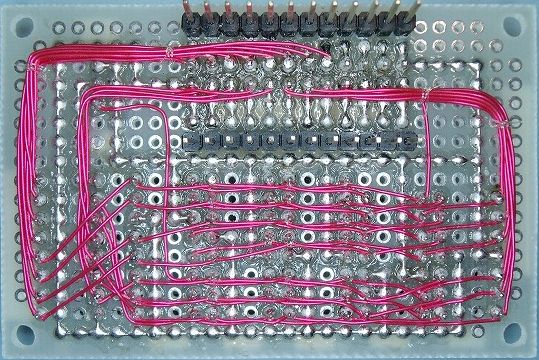

| 下側基板: コントロール部 | 上側基板: スイッチ操作・LED表示部 |

|

|

|

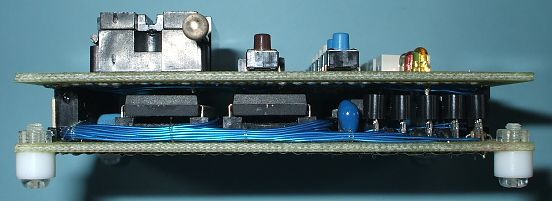

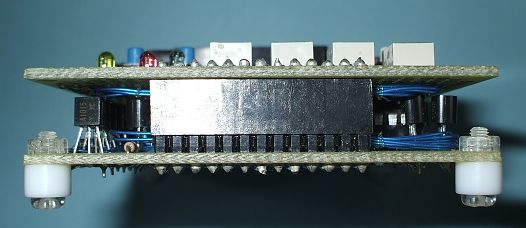

| 右側面から見る | 後側面から見る |

|

|

|

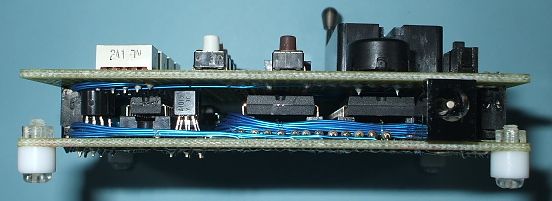

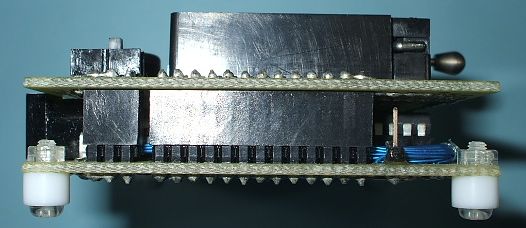

| 左側面から見る | 前側面から見る |

| ページトップ |

|

この簡易ロジックICチェッカ (Logic IC Checker)は、「各種スイッチ入力,

7セグ LED 表示部」 (以下、U1という。)、「各種ロジックICチェック, 結果表示部」

(以下、U2という。)、および 「各種ロジックICチェック補助制御部」 (以下、U3と

いう。) の三部からなっている。 ◇◇◇ U1:各種スイッチ入力, 7セグ LED 表示部 の機能 ◇◇◇ |

| ◇◇◇ U2:各種ロジックICチェック, 結果表示部 の機能 ◇◇◇ |

|

| ◇◇◇ U3:各種ロジックICチェック補助制御部 の機能 ◇◇◇ |

|

| ページトップ |

|

U1: PIC16F628A 用 ソースファイル (LogicIC_Checker1.asm) HEX ファイル (LogicIC_Checker1.hex) U2: PIC18F452 用 ソースファイル (LogicIC_Checker2.asm) IC データ ファイル (LogicIC_Table.inc) HEX ファイル (LogicIC_Checker2.hex) U3: PIC16F877A 用 ソースファイル (LogicIC_Checker3.asm) HEX ファイル (LogicIC_Checker3.hex) |

|

U2: PIC18F452 用のプログラム(ソースファイル(LogicIC_Checker2.asm))内で使用する、テーブルデータ(IC データ ファイル (LogicIC_Table.inc))

内には、大別して デバイス番号テーブル (dev_no_table) と、デバイスチェック・データテーブル (dev_ck_table)

との2つが存在する。 デバイス番号テーブルには、基本的にロジックICの種類(74シリーズ、4000シリーズ、4500シリーズのデバイス番号)数だけのデータが必要であるが、 ワンショット発生等の一部のICについては割愛してある。 また、デバイスチェック・データテーブルについては、個々のロジックIC別に必要とするチェック・データを用意してあり、複雑な働きをするICについてはその分 チェック・データも多く必要とし、テーブル全体としては膨大なデータ量となっている。 |

|

1. デバイス番号テーブル (dev_no_table)

1データ群は5バイトから構成されており、先頭の2バイトに4桁の デバイス番号 が設定されていて、

「U1:各種スイッチ入力, 7セグ LED 表示部 の機能」 から送られてきた、スイッチ入力されたデバイス番号と比較照合するのに使用される。

比較照合は5バイト単位の全テーブルデータとの間で行なわれる。

一致デバイス番号があった場合は、以降の3バイトデータを下図のようにそれぞれのレジスタに一旦保存して、次のデバイスチェック・データの読み出しに備える。

( 使用例 ) dt h'00', h'00' ;7400 Quad 2-Input NAND Gate dt h'00' dt high ic7400 dt low ic7400  [ フラグ・ビットの説明 ] |

|

2. デバイスチェック・データテーブル (dev_ck_table)

1データ群が何バイトから構成されているかは決まってなく、個々のロジックICの機能によってチェックデータが複雑に変化する、可変長データである。

|

| ページトップ |

|

本装置「汎用ロジック IC チェッカー」で、現在、チェックの確認がとれている74シリーズ、4000シリーズ、4500シリーズ ICの一覧を、

次表にまとめておきます。 なお、一覧表から各デバイスのデータシートも簡単に見られるように、リンクが貼ってあります。 << 対応デバイス一覧 >> (すみません。サーバ容量不足のため、データシートはありません。) |

|

|

|

| プリント基板(1)パターン図 (部品面) (LogicIC_Checker1PC.CE3) | ページトップ |

|

|

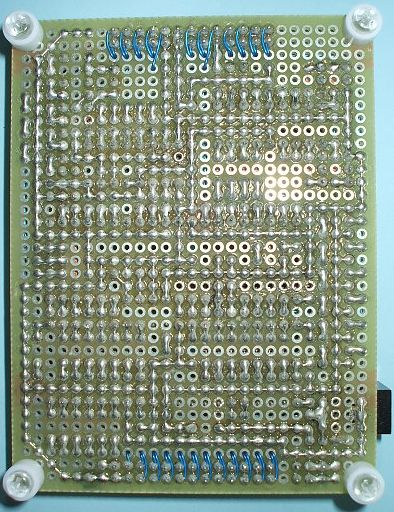

| プリント基板(1)パターン図 (ハンダ面) (LogicIC_Checker1PC1.CE3) | ページトップ |

|

|

| プリント基板(2)パターン図 (部品面) (LogicIC_Checker2PC.CE3) | ページトップ |

|

|

| プリント基板(2)パターン図 (ハンダ面) (LogicIC_Checker2PC1.CE3) | ページトップ |

|

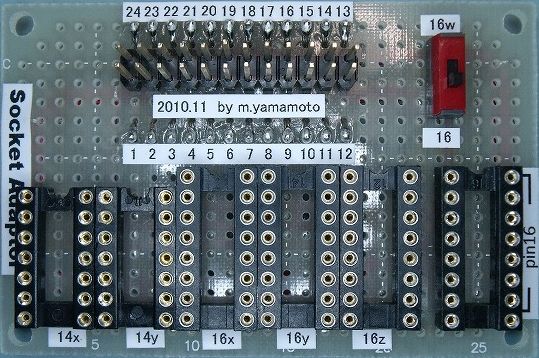

通常の対角線上の電源(Vcc, GND)ピン配置と異なって、 特殊な電源ピン配置となっているようなデバイス用に、汎用の 24 pin ゼロプレッシャー・ソケット

だけでは不十分なため、プリント基板(2) においては 16 pin の補助ソケットを 1個搭載してあります。 しかし、その補助ソケットでも pin14x, pin14y, pin16x 用には、挿入位置の変更だけで対処できますが、pin16y 用になると GND(Vss) ピンの変更が、pin16z 用では Vcc, GND 両ピンの変更が必要となります。 しかも、その変更を実現することは、一般的に運用時には容易ではありません。 また、披チェックデバイスによってはそのままの素の状態ではダメで、必要なジャンパーを外部に施した状態でチェックを行なわなければならないものもあります。 そこで、特殊な電源ピン配置とジャンパー施工との両方を考慮して、ピンヘッダを設けた特殊電源ピン・ソケットアダプタを、新たに作製(2010/11)しました。 プリント基板(3) の裏面にある 12 pin x 2 本のピンヘッダを、次の写真のように既設のゼロプレッシャー・ソケットに挟んで、三段構成にして使用します。

pin14x, pin14y, pin16x, pin16y, pin16z 用には、それぞれ専用のソケットを設けてあり、該当の特殊ピン披チェックデバイスをそのまま挿入するだけでOKです。 また、pin16w 用には一番右側の pinxxx ソケットを使用して、その上にあるスライドスイッチを上側に ON します。 この pinxxx ソケットは、スライドスイッチを下側に OFF しているときは 一般の pin16 用にも使用ができ、pin14 用のときもジャンパー施工を伴うような場合には、24 pin のピンヘッダとともに使用します。 なお、このアダプタの機能を使用するためには、U1でのデバイス番号の指定に例外入力をすることに注意をします。 74シリーズにおいても4000シリーズにおいても、 先頭は "9" で、それによって特殊ピンデバイスのデバイス番号の重複はありません。(先頭 "9": 例、7492 → 9092、4049 → 9049) ただし、ジャンパー施工を伴う一般のピン配置の pin14, pin16 用を使用する場合はその限りでなく、通常のデバイス番号の入力指定で行ないます。 現在把握している、特殊ピンデバイスやジャンパー施工を伴うデバイスの例を、次に挙げておきます。

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ページトップ |

|

|

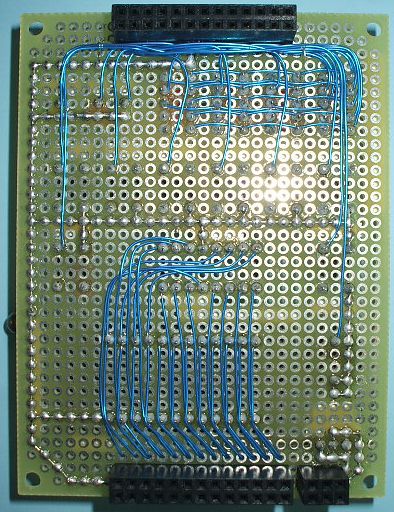

| プリント基板(3)パターン図 (部品面) (SpcSocketPC.CE3) | ページトップ |

|

|

|

| プリント基板(3)パターン図 (ハンダ面) (SpcSocketPC1.CE3) | ページトップ |

| (主要部品: IC, トランジスタ等) | (データシート) | ||

| PICマイコン | .................... | PIC16F628A | |

| PICマイコン | .................... | PIC16F877A | |

| PICマイコン | .................... | PIC18F452 | |

| 3-8 デコーダー | .................... | HD74HC138 | |

| トランジスタ | .................... | 2SA1015 | |

| ショットキダイオード | .................... | 1S4 | |

| 7セグメント LED | .................... | LNM213A | |

| 部品表

| Excel ファイル (LogicIC_Checker_parts.xls)

| ページトップ |

簡易型汎用ロジックICチェッカ .....

http://junneko.private.coocan.jp/hardware/checker/checker.htm

| ページトップ | ホーム |